# PAPER DETAILS

TITLE: Forming and Co-simulation of Square and Triangular Waveforms by Using System

Generator

AUTHORS: Ali ARSERIM, Cem HAYDAROGLU, Hüseyin ACAR, Aysegül UÇAR

PAGES: 337-341

ORIGINAL PDF URL: https://dergipark.org.tr/tr/download/article-file/773586

# Forming and Co-simulation of Square and Triangular Waveforms by Using System Generator

M.A. ARSERIM, C. HAYDAROĞLU, H. ACAR and A. UÇAR

Abstract—Nowadays Field Programmable Gate Arrays(FPGAs) are used to implement several processes in different areas such military defense, medical devices, automation, telecommunication, and image processing etc. Some of the advantages of FPGA are parallel and hardware processing. On the other hand programming FPGAs by classic design methodologies requires much effort. Therefore, design tools like System Generator can provide facilities about programming FPGAs. System Generator is a design tool from Xilinx to program the Xilinx FPGAs in MATLAB/Simulink graphic based editor. Also its block set is limited with respect to Simulink, has.

In this study square, and triangular waveforms are built with the basic blocks of System Generator tool. These waveforms belong to basic sources for signal processing. Generally, they are used in power electronics especially for producing PWM, or sinus PWM. Also co-simulation can be done by using System Generator. Square waveform block, which is implemented, has variable amplitude, frequency, duty cycle, and offset values whereas triangular waveform has variable amplitude, frequency, and offset values. Triangular waveform has an error as 2 % due to data bus width.

*Index Terms*— FPGA, waveforms, co-simulation, BASYS3 FPGA Board.

## I. INTRODUCTION

**F**PGA belongs to Programmable Logic Devices(PLDs) and is a very large scaled integrated circuit(VLSI)[1] Also FPGA is formed as a matrix of configurable logic block which can be connected to each other via fully programmable

MUHAMMET ALİ ARSERİM, is with Department of Electrical Engineering, University of Dicle, Diyarbakır, Turkey, (e-mail: <u>marserim@dicle.edu.tr</u>). https://orcid.org/0000-0002-9913-5946

**CEM HAYDAROĞLU**, is with Department of Electrical Engineering University of Dicle, Diyarbakır, Turkey, (e-mail: <u>c.haydaroglu@dicle.edu.tr</u>). https://orcid.org/0000-0003-0830-5530

HÜSEYİN ACAR, is with Department of Electrical Engineering, University of Dicle, Diyarbakır, Turkey, (e-mail: <u>hacar@dicle.edu.tr</u>). https://orcid.org/0000-0001-5127-4632

**AYŞEGÜL UÇAR**, is with Department of Mechatronics Engineering, University of Fırat, Elazığ, Turkey, (e-mail: <u>agulucar@firat.edu.tr</u>). https://orcid.org/0000-0002-5253-3779

Manuscript received December 31, 2018; accepted June 27, 2019. DOI: 10.17694/bajece.505842

interconnections[2]. It's clocking rate can be multiples of 100 Mega Hertzs, which can be seen low with respect to computer has. Since it makes parallel processing, has capability of making operations as hardware, and consumes low power, it is preferred in todays's electronic devices such as led tv, mobile phones, modems, imaging devices etc. So processing rate of FPGA increase enormously.

System generator is a tool for MATLAB/Simulink graphicbased editor, which is provided by XILINX firm in order to program its FPGAs [4]. Therefore, previous knowledge about design methodologies, or hardware descriptive language shouldn't be necessary by using System Generator. Also System Generator tool has co-simulation choice. Cosimulation provides both processing validation of the algorithm in a hardware, and increase in simulation speed. However, the number of Xilinx blocks are limited with regarding to Simulink blocks. In co-simulation process all of the Xilinx specific blocks are implemented and run in the target FPGA.

A periodic waveform is a waveform which repeats itself in time. Periodic waveforms are important in electronic circuits, and can be used for different purposes such as clocking, switching, triggering, producing different wave shapes as PWM signal vice versa [5]. Besides basic periodic waveforms are sine, square, rectangular, triangular, saw tooth, and pulse waveforms.

In this study it is aimed to implement two new blocks as square and triangular waveform for System Generator by using existed Xilinx specific blocks in Simulink. Several parameters as amplitude, frequency, and offset of these blocks can be tuned. After all, co-simulation is done for validation.

## II. MATERIALS AND METHODS

Square and triangular periodic waveforms are two of the basic waveforms used in electronic circuits. They can also be used in power electronics for different purposes.

#### A. Square waveform

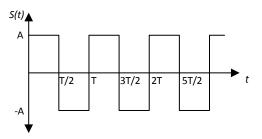

Square wave is a type of periodic waveform which alternates between two levels [6]. It is shape is given in Fig 1

Fig. 1. Square waveform

and described as

$$S(t) = A(-1)^{floor(2(t-t_0)/T)} + d$$

(1)

Where: A - is amplitude;

*f floor* – is floor function;

t - is time, [s];

- $t_o$  is offset, [s];

- T- is period, [s];

- d is offset in amplitude;

Also square waveform can be used as a pulse train if its amplitude changes between A and 0. Besides duty cycle can be changed and PWM signal is obtained.

# B. Triangular waveform

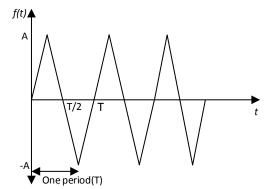

Triangular wave is a non-sinusoidal two directional waveform [5]. It is linearly increases, and decreases between these two points. and it is alternated between two points by a ramp shape. Triangular waveform is shown in Fig.2

# It is defined as

$$f(t) = \begin{cases} \frac{2A}{T}(t-nT) & 0+nT < t < \frac{T}{2} + nt & n = 0, \mp 1, \mp 2, \dots \\ \frac{-2A}{T}(t-\frac{T}{2} - nT) + A & t + \frac{T}{2} + nT \le t < t + \frac{3T}{2} + nT & n = 0, \mp 1, \mp 2, \dots \\ \frac{2A}{T}(t-\frac{T}{2} - nT) - A & t + \frac{3T}{2} + nT \le t < t + 2T + nT & n = 0, \mp 1, \mp 2, \dots \end{cases}$$

Where: A - is amplitude;

n – period number

- t is time, [s];

- T- is period, [s];

Also an offset value, or time delay can be added to the signal. In practise triangular waveform can be obtained by electronic circuits. Examples of such circuits are operational

Copyright © BAJECE

transresistance amplifier (OTRA) and current feedback operational amplifier [7,8]. Besides triangular waveform can be implemented by using up-down counter in software tools. Also look up tables can be used for any desired signal shape [9].

# C. System Generator

System Generator is tool provided by Xilinx firm for MATLAB/Simulink, for programming its FPGAs visually. Xilinx blockset is added to Simulink by System Generator, and a Simulink model can be implemented with consisting of Xilinx specific blocks, and then FPGA program is built automatically. Therefore, there is no need to know programming language, and design methodologies [4].

If it is desired to make simulation with Xilinx blocks, initially System Generator icon should be added to the model. A window, which is shown in Figure 3, to make the various settings is open after double clicking this icon. In this window FPGA type, clock rate, operation type is chosen.

| 🚯 System Generator: ucgen                               |                     |                  | -        |             | ×          |

|---------------------------------------------------------|---------------------|------------------|----------|-------------|------------|

| ompilation Clocking Gener                               |                     |                  |          |             | 1          |

| Board :                                                 | ai                  |                  |          |             |            |

| > Basys3 C.0                                            |                     |                  |          |             |            |

| Part :                                                  |                     |                  |          |             |            |

| > Artix7 xc7a35t-1cpg236                                |                     |                  |          |             |            |

| Compilation :                                           |                     |                  |          |             |            |

| > Hardware Co-Simulation (JTAG)                         |                     |                  |          |             | Settings . |

| Hardware description langua                             | ge:                 | VHDL libra       | ry :     |             |            |

| VHDL                                                    | ~                   | xil_defaultlib   |          |             |            |

| Use STD_LOGIC type for Boolean of<br>Target directory : | or 1 bit w          | de gateways      |          |             |            |

| ./netlist                                               |                     |                  |          |             | Browse.    |

| Synthesis strategy :                                    | Impl                | ementation s     | trategy  | :           |            |

| Vivado Synthesis Defaults ~                             | Vivad               | o Implementation | Defaults | ~           |            |

| Create interface document                               | Create testbench Mo |                  | Mode     | el upgrade. |            |

| Performance Tips Generate                               | ок                  | Apply            | Canc     | . 1         | Help       |

Fig. 3 System Generator window

Co-simulation option can be chosen, in order to make cosimulation with the specific FPGA. Vivado software runs in background to produce the bitstream file after pressing the Generate button. After all co-simulation can be done by loading bitstream file to FPGA.

# D. BASYS3 FPGA training card

BASYS3 has Xilinx Artix-7 architecture and is a cheap and entry-level FPGA development card for Vivado. It has 33280 logic cell and its clocking rate is 150 MHz. BASYS3 FPGA training card is shown in Figure 4[10].

Fig. 4 BASYS3 FPGA training card

# III. FINDINGS

In this study, periodic square and triangular waveform blocks are implemented by using Xilinx specific blocks in MATLAB/Simulink. Therefore, these blocks simulated and co-simulated.

Periodic square waveform, implemented with Xilinx blocks are shown in Figure 5

Fig. 5. Square waveform model wiht Xilinx specific blocks

Besides this model is masked and a block is created. The block parameters window is shown in Figure 5;

| Block Parameters: Subsystem                   |    |  |

|-----------------------------------------------|----|--|

| Subsystem (mask)                              | ^  |  |

| Parameters                                    |    |  |

| Amlitude(A) 50                                |    |  |

| Frequency(f) 50                               |    |  |

| Duty Cycle(TD) 50                             |    |  |

| Offset(d) 0                                   | ~  |  |

| OK Cancel Help Apply                          | /  |  |

| Fig. 6. square waveform block parameters wind | ow |  |

Here amplitude, frequency, offset of the square waveform can be adapted. Also, if it is desired to use this block as a PWM signal generator there is an option for duty cycle.

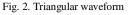

In the application firstly, this block is simulated with the parameters for peak amplitude, frequency, and offset as 50, 50, and 0 respectively. Then co-simulation block of square waveform is generated by System Generator and added to the model as shown in Figure 7;

Fig. 7 The square waveform model with co-simulation block

As mentioned above, triangular waveform is built with the Xilinx specific blocks as shown in Figure 8;

Fig. 8. Triangular waveform model with Xilinx specific blocks

In this model an up-counter is used for control logic, and one up-counter and one down-counter is used for forming triangular wave. Later amplitude, and offset of this wave is adapted. Thus, this model is masked, and then triangular waveform block is built. Block parameter window of this block is shown in Figure 9;

| Block Parameters: Subsystem                        | $\times$ |  |  |  |  |

|----------------------------------------------------|----------|--|--|--|--|

| Subsystem (mask)                                   | ^        |  |  |  |  |

|                                                    |          |  |  |  |  |

| Parameters                                         |          |  |  |  |  |

| Frequency(f) 50                                    |          |  |  |  |  |

| Amplitude(A) 50                                    |          |  |  |  |  |

| Offset(d) 0                                        |          |  |  |  |  |

| number of samples(N) 1000                          | ~        |  |  |  |  |

| OK Cancel Help Apply                               | ·        |  |  |  |  |

| Fig. 9. Triangular waveform block parameter window |          |  |  |  |  |

In this window frequency, amplitude, offset, and step size of the counters can be adapted.

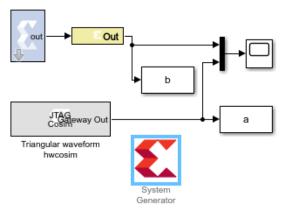

Therefore, frequency, amplitude, offset, frequency, and step size of the counters are selected as 50, 50, 0, and 1000 respectively. The model with co-simulation block, generated is shown in Figure 10;

Fig. 10. The triangular waveform model with co-simulation block

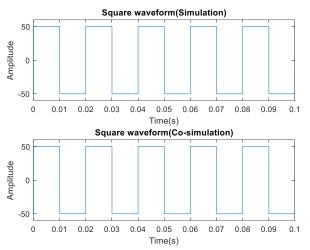

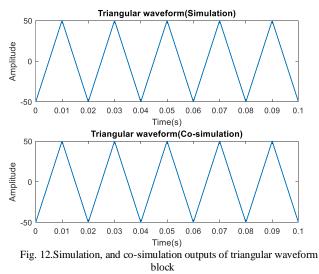

Two models are run and simulation, and co-simulation results for square, and triangular waves are obtained as in Figure 11, and 12 respectively.

Fig. 11. Simulation, and co-simulation outputs of square waveform block

It can be seen from the figures 11, and 12 that simulation, and co-simulation results are same for both square, and triangular waveforms. This means that validation for the associated hardware is performed. Also in detailed analysis of the waveforms, there is an error as % 1.2 in the amplitude of triangular waveform. This error is occurred to the signed number bit bus width of block. Also, the error can be decrease by increasing the bit bus width, or using floating point math.

#### IV. CONCLUSION

In this study it is aimed to add two new blocks as square and triangular waveforms to Xilinx blockset, provided by System Generator, in MATLAB/Simulink graph-based editor.

Also, these waveforms are among fundamental signals in electronics. Square waveform has harmonics of basic frequency, so it can be uses in harmonic analysis. In addition, this block has an extra choice as duty cycle. So this wave can be used as square wave PWM.

Triangular wave can be used in sinus PWM. Resulted signal of the block is satisfactorily from the viewpoint of sampling number, and the shape of the signal. Besides, BASYS3 FPGA card has a 100 MHz clock rate. So it can support PWM signals with high speed, and resolution.

Co-simulation results shown that the card can be used as a signal generator in practical circuits. This card can be used with Pmode (Peripheral mode) accessories for real time applications. Since FPGA can make parallel operations, this card can be used as multiple signal generator due to the range of Pmode accessory outputs.

Finally, this two block is sent to Xilinx Firm with the hope of contribution to Xilinx blockset provided by System Generator to MATLAB/Simulink.

#### Acknowledgment

The authors thank to Xilinx firm for Vivado design suite program licenses, and BASYS3 FPGA training cards.

#### References

- [1] C. Maxfield, "The design warrior's guide To FPGAs: Devices, Tools And Flows." Elsevier, 2004.

- [2] E. Monmasson, M.N Cirstea, "FPGA design methodology for industrial control systems-a review", IEEE Transactions On Industrial Electronics, Vol. 54, No. 4, 2007, pp.1824-1842.

- [3] E. Sarıtaş, S. Karataş. "Her yönüyle FPGA ve VHDL" Palme, 2013.

- [4] https://www.xilinx.com/support/documentation/sw\_manuals/xilinx2017 \_2/ug897-vivado-sysgen-user.pdf

- [5] https://www.electronics-tutorials.ws/waveforms/waveforms.html.

- [6] http://mathworld.wolfram.com/SquareWave.html

- [7] Y. Lo, H. Chien., "Switch-controllable OTRA-based square/triangular waveform generator.", IEEE Transactions On Circuits And Systems II: Express Briefs, Vol.54, No. 12, 2007, pp. 1110-1114.

- [8] A. S., Haque, M. M. Hossain, , W. A. Davis, , H. T. Russell, & R. L. Carter, "Design of sinusoidal, triangular, and square wave generator using current feedback operational amplifier (CFOA)", In Region 5 Conference, 2008 IEEE, pp. 1-5.

- [9] M. Lakka, E. Koutroulis, A. Dollas, "Development of an FPGA-based SPWM Generator for high switching frequency DC/AC inverters" IEEE Transactions on power electronics, Vol.29, No.1, 2014, pp. 356-365.

- [10] https://store.digilentinc.com/basys-3-artix-7-fpga-trainer-boardrecommended-for-introductory-users/.

# **BIOGRAPHIES**

Muhammet Ali ARSERİM Şanlıurfa City, Turkey, in 1975. He received the B.S. degree in Electrical & Electronics Engineering from the University of Çukurova, Adana, Turkey, in 1999, M.S. degree in Electrical & Electronics Engineering from the University of Dicle, Divarbakır, Turkey, in 2001 and the Ph.D. degree in Electrical & Electronics

Engineering from the University of Fırat, Elazig, Turkey, in 2009.

From 1998 to 2011, he was a Research Assistant with the Electrical & Electronics Engineering Department from the University of Dicle. Since 2011, he has been an Assistant Professor with the Electrical & Electronics Engineering Department from the University of Dicle. He is the author of several articles. His research interests include image processing, embedded systems and applications, FPGA, and system design.

Cem HAYDAROĞLU, Elazığ City, Turkey, in 1989. He received the B.S. degree in Electrical & Electronics Engineering from the University of Fırat, Elazığ, Turkey, in 2011, M.S. degrees in Electrical & Electronics Engineering from the University of Dicle, Diyarbakır, Turkey, in 2017. He is currently PhD student in Dicle University, Electrical & Electronics

Engineering.

From 2014 to present, he is a Research Assistant with the Electrical & Electronics Engineering Department in Dicle University. His research interests are smart grids, power system analysis.

Hüseyin ACAR, Midyat, Mardin City, in 1983. He received the B.S. degree in Electronics Engineering from Uludağ University, Bursa, Turkey, in 2006, M.S. degree in Electrical & Electronics Engineering from Dicle University, Diyarbakır, Turkey, in 2010. He is currently PhD student in Dicle University

Electrical & Electronics Engineering.

From 2007 to present, he is a Research Assistant with the Electrical & Electronics Engineering Department at Dicle University. His research interests remote sensing, image processing and embedded systems.

Ayşegül UÇAR received a BS degree, MS degree, and PhD degree from the Electrical and Electronics Engineering Department at the University of Firat of Turkey in 1998, 2000, and 2006, respectively. In 2013, she was a visiting professor at Louisiana State University in the USA. She has been an associate

professor in the Department of Mechatronics Engineering since 2014. Her research interests include modeling and control, artificial intelligence systems, robotics vision, pattern recognition, and signal processing.