# PAPER DETAILS

TITLE: An Electronically Tunable Low Power Low Pass Filter Employing Capacitor Multiplier for

**Biomedical Applications**

AUTHORS: Deniz ÖZENLI, Ersin ALAYBEYOGLU

PAGES: 845-861

ORIGINAL PDF URL: https://dergipark.org.tr/tr/download/article-file/2471647

ISSN: 1307-9085, e-ISSN: 2149-4584

Araştırma Makalesi

Erzincan University

Journal of Science and Technology

2022, 15(3), 845-861

DOI: 10.18185/erzifbed.1127213

Research Article

# An Electronically Tunable Low Power Low Pass Filter Employing Capacitor Multiplier for Biomedical Applications

Deniz Özenli<sup>1,3</sup>, Ersin Alaybeyoğlu<sup>2,3\*</sup>

<sup>1</sup>Department of Electronics Engineering, Turkish Air Force Academy, National Defence University, Istanbul, 34149, Turkey

<sup>2</sup>Electrical and Electronics Engineering, Bartın University, Bartın, Turkey <sup>3</sup>Electrical and Communication Engineering, Istanbul Technical University, Istanbul, Turkey

**Received:** 07/06/2022, **Revised:** 03/07/2022, **Accepted:** 14/07/2022, **Published:** 30/12/2022

#### **Abstract**

In this work, a novel 0.9nW low pass filter is proposed using 0.18 $\mu$ m TSMC technology in Cadence environment to reject unwanted signals of biomedical applications. Active RC filter is designed with a new capacitor multiplier implementation providing high multiplication factor along with low power consumption. The designed circuit operates with  $\pm 0.3$ V supply voltages with DTMOS technique. At the same time, the power consumption of the proposed circuit is very low that can be implemented in implantable devices. The bandwidth of the designed filter is adjustable between 500mHz and 65Hz. In terms of Figure of Merit, the proposed filter outperforms the recommended circuits in the literature.

**Keywords:** Biomedical Applications, Low Pass Filter, Operational Transconductance Amplifier (OTA), Dynamic Threshold MOS (DTMOS)

# Biyomedikal Uygulamalar için Kapasite Çarpıcı Kullanan Elektronik Olarak Ayarlanabilen Düşük Güçlü Alçak Geçiren Süzgeç

### Öz

Bu çalışmada, biyomedikal uygulamaların istenmeyen işaretleri süzmek için Cadence ortamında 0.18µm TSMC teknolojisi kullanılarak yeni bir 0.9nW düşük geçiş filtresi önerilmiştir. Aktif RC filtresi, düşük güç tüketimi ile birlikte yüksek çarpma faktörü sağlayan ve üç katmalı OTA yapısından oluşan yeni bir kapasite çarpıcı devresi ile tasarlanmıştır. Tasarlanan filtrenin bant genişliği 500mHz ile 65Hz arasında ayarlanabilmektedir. Aynı zamanda önerilen devrenin güç tüketimi taşınabilir cihazlarda uygulanabilecek kadar düşüktür. Önerilen kapasite çarpıcı devresi özellikle güç tüketimi ve çalışma gerilimi açısından literatürde önerilen devrelerden daha yüksek performans göstermektedir.

Anahtar Kelimeler: Biyomedikal Uygulamalar, Alçak Geçiren Süzgeç, OTA, DTMOS

### 1. Introduction

Today, the demand for wireless devices such as portable biomedical devices, smartphones, laptops, tablet computers, and various wireless devices is constantly increasing. Integration of system plays a role as important as power dissipation for portable devices. Industry 4.0 applications will further expand the use of mobile devices [1]. The portability of digital circuits is increased by the CMOS technology produced in small dimensions. However, the fact that CMOS transistors produced in small sizes cannot be used effectively in analog circuit design has led to the search for new methods to design analog circuits [1,2].

CMOS technology is ideal in terms of the circuit, which needs to be designed with low power consumption. The minimized supply voltage is functional to reduce the power consumption of the circuits. The threshold voltage cannot be downscaled by the same extent as the supply voltage in modern small size CMOS technologies gets smaller. The high V<sub>TH</sub> is required to obtain a low current when the transistor is switched off. The current injection of MOSFETs is generally in several nano amper ranges in the weak inversion region that will be functional due to a minimized supply voltage [3,4]. Also, the circuit topology must be suitable for the minimized supply voltage. The above requirements encourage the innovative design strategies in CMOS analog circuit design [5-8]. For example, the Dynamic Threshold MOS (DTMOS) technique is an example of new design strategies proposed for CMOS technology [9,10]. Particularly, low power consumption has increased the importance for the circuits used in the Internet of Things applications that are becoming widespread in our lives [11,12].

In biomedical signal acquisition systems, low frequency filters are used to reject unwanted signals and extract low frequency bio-potential signals. The rejection of out-of-band noise and interference suppression is realized by using these low frequency filters [13,14]. Bio-potential signals are weak analog signals. The amplitude of bio-potential signals extends between  $1\mu V$  to 10mV while the frequency of bio-potential signals ranges from less than 1Hz to 10kHz [15]. In the integration of low pass filters operated at low frequencies, the filter topology of RLC and RC are not practical due to the high costs [16]. Switched capacitor filters are not preferred to collect bio-potential signals because they are affected by leakage currents in the switching [17]. In biomedical systems, to catch the low frequency operation,  $G_m$  - C filters are widely used [18]. In  $G_m$  –C filters, the cut-off frequency is determined by the  $G_m$  / C ratio, where  $G_m$  is defined as the transconductance of the operational trans-conductance amplifier (OTA) and C is integrated capacitor. To implement the filter at low cut-off frequencies, large valued C and pretty small  $G_m$  are preferred. In this respect, various design techniques have been proposed in the literature to obtain low  $G_m$  to OTAs [19,20].

However, capacitance multiplier circuits are commonly used for applications described in the literature as sub-hertz [21-23]. In an RC network, circuits operating at low frequencies are designed by increasing the time constant with a huge value of resistance or capacitance. To improve the time constant of RC network, the multiplied capacitance can be implemented instead of conventional capacitor.

In this study, a low pass filter is designed to meet the wireless features of biomedical applications, with a wide range of settings based on capacitor multiplier. The design consumes very low power, suitable for bio-potential signal acquisition systems used in the applications of Internet of Things. The presented circuit is implemented with DTMOS transistors in subthreshold region. Meanwhile, supply voltages of the design are  $\pm 0.3 V$ . Overall simulations are realized in Cadence environment. Also, the performance of the circuit is verified using  $0.18 \mu m$  TSMC technology.

This paper is organized as follows. In the second section, circuit design of the capacitance multiplier is given. In the third section, the CMOS realization of capacitor multiplier is given

while second order Butterworth filter structure and its layout are given in forth section. Transient and AC analysis of the designed filter are given in forth section with noise analysis. Additionally, the performance of the designed filter is justified by comparing conventional designs in terms of Figure of Merit. Section V gives some conclusions.

## 2. Circuit Design of Proposed Capacitance Multiplier

One of the most limiting problems in the design of integrated circuits is the large area occupation on the integration of passive circuit elements such as resistance, inductance and capacitance. Continuous time applications in which the use of component (R, L and C) multipliers is inevitable have to deal with the problem of integration of high-value passive circuit elements. There is widespread research in the literature on this critical issue. In this respect, the design of capacitance multiplier circuits is of greater importance than others. Although it is used in RF designs with the general acceptance of inductance, capacitor is an indispensable circuit element in most of circuits such as capacitive low frequency filters, analog to digital converters, and digital to analog converter. In particular,  $G_m - C$  filters including multiplier structures have been widely used in the literature. Such capacitance multiplier circuits have attractive properties of temperature insensitive C-values with good stability [24–27].

The categorization of capacitor multipliers designed in the literature can be divided to two parts as voltage and current-mode. The voltage-mode capacitor multiplier circuits are generally used for frequency compensation. In this regard, capacitor multipliers designed with operational amplifiers can be given as an example of voltage mode multipliers. The current mode multipliers can be designed with CCII, OTA and etc. The second generation current conveyor (CCII) has also been used to realize C-multiplier circuits due to its attractive characteristics [22,28]. Even though CCII are suitable for the multiplier design with high multiplication factor, OTAs are more attractive building blocks for the reconfigurable design of multiplication factor. A large number of OTA-based C-multiplier circuits using bias adjustment have been reported in literature [27,29].

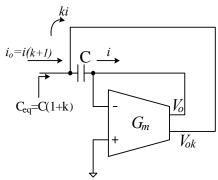

Figure 1. OTA based capacitor multiplier.

The simplest OTA based capacitor multiplier reported as current mode is shown in Figure 1, while the proposed circuit is given in Figure 2. The first and second OTAs used in the implementation of the multiplier have multiple current outputs. In this topology, "i" on C is sensed with the low value of  $G_{m1}$ . Multiplication of the sensed current by multiplication factor denoted as k, is obtained with higher gain of  $G_{m1}$ .  $G_{m2}$ .  $G_{m3}$ .  $R_{o1}$ .  $R_{o2}$  where  $R_o$  denotes the output impedances of the each OTA. In this respect,  $i_o$  is equal to "i" times (1 + k), while  $C_{eq}$  is equal to the C. (1 + k). As a result, output current shown as  $i_o$  in the Figure 2, gives k times higher value of the current in (1) approximately. It should be noted that this simple scheme based on traditional topology provides good accuracy in spite of limited multiplication factor

and allows only single-ended applications, whereas the current multiplication inside single OTA with current mirror or other methods increases the consumption of power and the occupation area on the silicon [30].

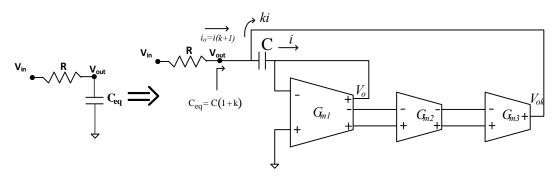

Figure 2. Proposed filter with capacitor multiplier.

This proposed topology is developed version of OTA based multipliers reported in literature [27], [31]. In this topology, the multiplied current k. i is obtained with three cascaded OTA. The non-inverting output of the first cell gives  $V_o$ , while  $V_{ok}$  is the non-inverting output of third cell. The third OTA is driven with the fully differential output of second OTA, while the fully differential output of first OTA drives the second OTA. The multiplication factor of k is maximized by selecting the conductivity of the second and third cell as high as possible. The equation of i is given in (1).  $G_m$  defines the transconductance of OTA, where  $V_P$  is non-inverting input of OTA and  $V_N$  is inverting input of OTA as well.

$$i = G_{m1}(V_P - V_N) \tag{1}$$

In this respect, taking into consideration output impedances of the OTAs, impedance seen from  $V_{out}$  node can be given in the following form:

$$Z = \frac{sC + G_{m1}}{sC(G_{m1} + 4R_{o1}R_{o2}G_{m1}G_{m2}G_{m3})} / / R_{o3}$$

(2)

In the subthreshold operation, very high output impedances of OTAs can be obtained. Hence, for the simplicity of calculations, third OTA's output impedance can be ignored. Furthermore, in the low operating currents with the help of DTMOS technique,  $G_{m1}$  can be easily tuned from a few nS up to a couple of 10 nS. For the base capacitance (C) values in the range of a couple of 10pFs, (2) can be easily simplified as follows for the biomedical applications with the operating frequency up to around 100Hz:

$$Z \cong \frac{G_{m1}}{sC(G_{m1} + 4R_{o1}R_{o2}G_{m1}G_{m2}G_{m2})}$$

(3)

Moreover, if  $G_{m1}$  is increased up to 10nS, (3) keeps capacitance multiplier behavior up to 10kHz approximately. In this point of view, "k" multiplication factor can be approximated as follows:

$$k \cong 4R_{01}R_{02}G_{m2}G_{m3} \tag{4}$$

$$\omega_{cut-off} \cong \frac{1}{kRC} \tag{5}$$

In this view, (4) brings a large amount of capacitance value at the  $V_{out}$  node to attain very low operating frequency region in the biomedical applications. According to (4) and (5), cut-off frequency of the proposed first order low pass filter can be safely adjusted by output impedances and transconductance values of the three cascaded OTA stages. Hence, bias currents of the OTAs play an important role in determining the cut-off frequency of the proposed filter with capacitance multiplier. In the next sections, DTMOS technique is given with the CMOS implementation of the OTAs, whereas the operating mechanism of the filter is justified with the post layout simulations with regard to different bias currents of each OTAs.

## 3. CMOS Implementation of Low Pass Filter

Biomedical applications such as implantable and portable devices must be provided with low power operation. MOS transistors operating in deep sub-threshold region consume very low power. Generally, the designed circuits in sub-threshold region designed with MOS transistors have low supply voltage. For example, when the supply voltage of designed circuit with saturated MOS transistors for the 0.18µm technology is 1.8V, the supply voltage of this circuit with MOS transistors in weak inversion region for the 0.18µm technology can be lower than 0.7V.

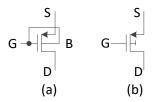

Moreover, to improve the performance of the MOS transistors with the same power dissipation, different techniques such as Dynamic Threshold Metal Oxide Semiconductor (DTMOS) are investigated in literature [9], [32]–[36]. DTMOS can support high current gain and with low threshold characteristics and its leakage current is minimized. Because of its ultra-low voltage capability, DTMOS is very practical to design ultra-low voltage analog circuits [37], [38]. The idea of DTMOS is established by connecting the transistor gate and body to each other. This connection changes the threshold voltage. The threshold voltage of DTMOS is given in (6). The proposed CMOS circuit is implemented with DTMOS transistors as given in Figure 4, whereas DTMOS realization symbol is illustrated in Figure 3.

**Figure 3**. (a) The realization of DTMOS with standard MOS (b) The representation of DTMOS

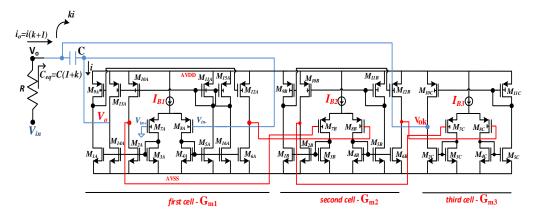

Figure 4. CMOS implementation of proposed filter.

$$|V_{th,p}| = |V_{th0,p}| + \gamma_p \left( \sqrt{|2\Phi_F| + V_{SB}} - \sqrt{|2\Phi_F|} \right)$$

(6)

The implementation of the proposed circuit is suitable to obtain high multiplication factor. The implementation of designed structure is advanced version of recently recommended cell-based variable transconductance amplifier [39], [40]. Three cascaded symmetric OTAs compose the structure. The first OTA is called "first cell" while the second OTA is "second cell" and the third one is "third cell". Table 1 gives the size of the transistors. In the proposed structure, the fully differential output is easily implemented by symmetrical OTA to drive the second and the third cells. In this respect, (7) gives the gain of each OTA in the sub-threshold region.

**Table 1.** The size of transistors.

| Transistors                                                                 | First Cell<br>W/L | Transistors               | Second Cell<br>W/L | Transistors                         | Third Cell<br>W/L |  |

|-----------------------------------------------------------------------------|-------------------|---------------------------|--------------------|-------------------------------------|-------------------|--|

| M <sub>1A</sub> , M <sub>2A</sub> , M <sub>5A</sub> , M <sub>6A</sub> ,     | 2μm/360nm         | $M_{1B},M_{2B},M_{5B},$   | 6μm/360nm          | M <sub>2C</sub> , M <sub>5C</sub>   | 6μm/360nm         |  |

| M <sub>9A</sub> , M <sub>10A</sub> , M <sub>11A</sub> ,<br>M <sub>12A</sub> | 2μm/360nm         | $M_{9B},M_{10B},M_{11B},$ | 6µm/360nm          | M <sub>10C</sub> , M <sub>11C</sub> | 6μm/360nm         |  |

| $M_{7A}$ , $M_{8A}$                                                         | 360nm/360nm       | $M_{7B}$ , $M_{8B}$       | 5μm/360nm          | M <sub>7C</sub> , M <sub>8C</sub>   | 5μm/360nm         |  |

| $M_{3A}$ , $M_{4A}$                                                         | 4μm/220nm         | $M_{3B}$ , $M_{4B}$       | 2μm/220nm          | M <sub>3C</sub> , M <sub>4C</sub>   | 2μm/220nm         |  |

| $M_{13A}, M_{14A}, M_{15A}, M_{16A}$                                        | 2μm/360nm         | -                         | -                  | -                                   | -                 |  |

$$K_{VO} = \frac{g_{m8} \cdot \frac{\left[\frac{W}{L}\right]_5}{\left[\frac{W}{L}\right]_4}}{g_{ds5} + g_{ds11}}$$

$$(7)$$

$g_m$  and  $r_o$  of MOS transistor are shown in (8) for the sub-threshold region.  $g_m$  defines the transconductance of transistor, while  $r_o$  is the output impedance of transistor.  $\kappa$  denotes the subthreshold gate efficiency, whereas  $\lambda$  is the parameter of channel length modulation.  $V_T = k.T/q$  is the thermal voltage (k - Boltzmann constant, T - absolute temperature, q - elementary charge).

$$g_m \cong \frac{\kappa. q. I_D}{kT}, \quad r_o = \frac{1}{\lambda I_D}$$

(8)

In the proposed circuit,  $V_o$  is obtained from the first cell with the transistors of  $M_{13A}$ ,  $M_{14A}$ ,  $M_{15A}$ ,  $M_{16A}$ ,  $M_{2A}$ ,  $M_{5A}$ ,  $M_{10A}$ ,  $M_{11A}$ , whereas  $V_{ok}$  comes from the third cell to increase the multiplication factor by passing through the first and second cells. The gain of (k + 1) is maximized to be as large as possible by this way. (6), (7) and (8) are used to determine the dimensions of the transistors in Figure 4.

# 4. Layout and Post-Layout Simulations

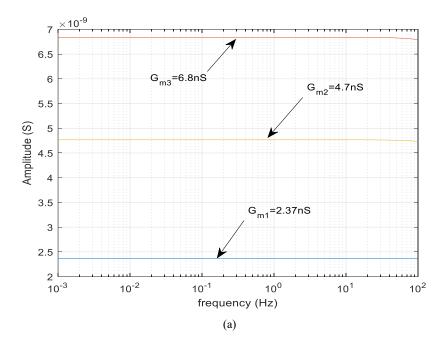

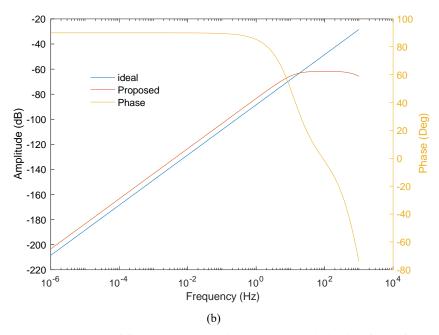

Minimum power consumption of the designed circuit is 0.98nW under the minimum biasing current. The simulated results for the transconductance of the cells in the proposed topology are illustrated in Figure 5 (a). In this respect, transconductance of the first cell can be observed around 2.37nS for  $I_{B1}$ =0.1nA current. Also, transconductance of the second cell is given as 4.7nS for  $I_{B2}$ =0.1nA, while transconductance of the third cell is found as 6.8nS for  $I_{B3}$ =0.1nA. Furthermore, multiplication factor for 10pF base capacitance is simulated as shown in Figure 5 (b). Multiplied capacitance is around 60nF, while the multiplication factor is 6000 with 90° phase response. According to Figure 5 (a) and (b), there is a good agreement between simulation results and equations of (2), (3), and (4) presented in the previous section.

**Figure 5**. (a) Transconductance of first, second and third cell, (b) multiplication factor for 10pF base capacitance.

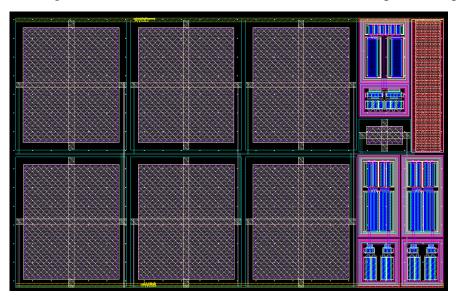

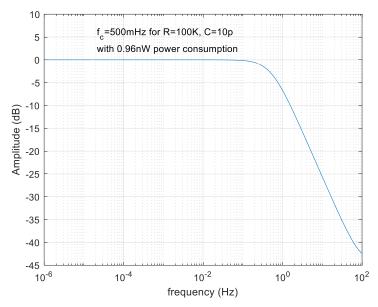

Figure 6 gives the layout of the designed filter. The occupied area on chip without electrostatic discharge (ESD) protection of the designed circuit is  $71.99\mu mx115.05\mu m$ ;  $0.0083mm^2$ . The post-layout simulation of the second-order low pass filter is shown in Figure 7. The cut-off frequency of the designed filter is 500mHz for  $100k\Omega$  resistance with 10pF base capacitance.

Figure 6. Layout of the proposed circuit (occupies 0.0083mm<sup>2</sup> area).

Figure 7. Post-layout simulation of designed filter for  $R=100k\Omega$  and C=10pF (base capacitor).

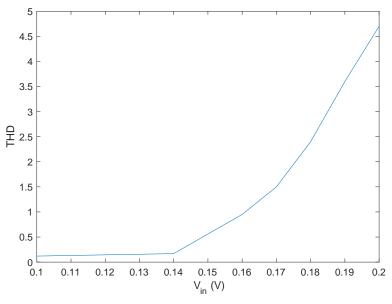

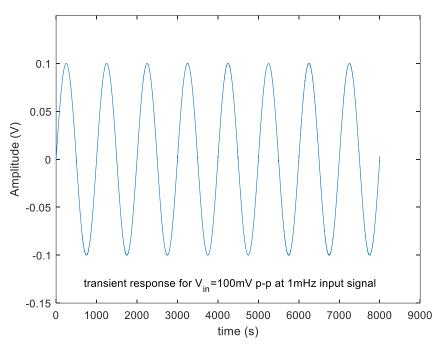

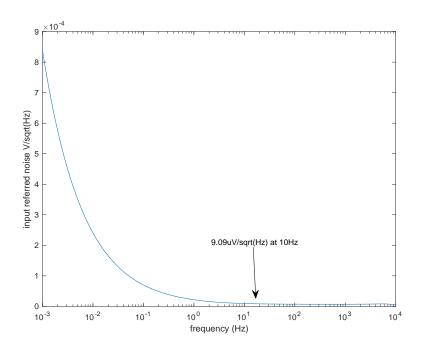

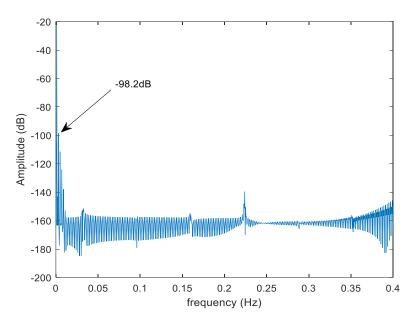

THD performance of the filter for peak-to-peak input signal at 1mHz frequency is given in Figure 8. The total harmonic distortion is 0.12% for 100mV peak-to-peak input signal at 1mHz, while output signal of the proposed filter is given in Figure 9 for the same input voltage signal. Furthermore, input referred noise is  $9.09\mu\text{V/sqrt}(\text{Hz})$  as given in Figure 10. Spurious Free Dynamic Range (SFDR) of the designed filter is around -78.2dBc. The analysis of SFDR is given in Figure 11 at 1mHz input frequency for 100mV peak to peak input signal.

Figure 8. Linearity check of the designed filter (THD = 0.12% for 100mV of peak input signal at 1mHz).

**Figure 9.** Transient response of the designed filter (THD = 0.12%).

Figure 10. Input referred noise of the designed filter.

Figure 11. Spurious Free Dynamic Range.

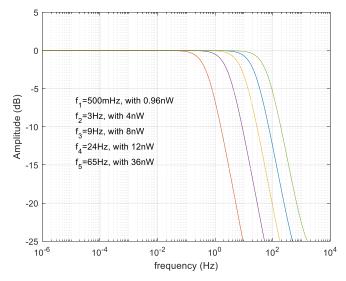

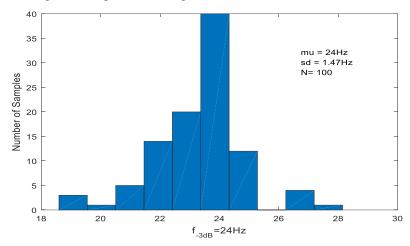

The cut-off frequency of the designed filter can be adjustable with the biasing current as given in Figure 12. Table 2 gives the biasing current of each cell versus f(-3dB) as well. The configurability of the designed filter can be realized by changing G<sub>m2</sub> and G<sub>m3</sub> with different I<sub>B2</sub> and I<sub>B3</sub>, respectively. Also, output impedances of the first and second OTAs in the proposed filter structure in Figure 2 play an important role for the cut-off frequency. In this point of view, Figure 12 and Table 2 are in good agreement with equations of (3), (4), (5), (7) and (8) presented in the previous sections. Corner analysis of the designed filter including variations of process (ss, tt, ff, sf, fs), temperature (-40°C, 85°C), and power supplies of AVDD and AVSS (0.33V, 0.27, -0.33V and -0.27V) is realized to check resilience of the performance. It can be said that the filter performance remains in acceptable limits. The low pass function of the designed filter is preserved under the worst cases. In addition, Figure 13 gives the Monte Carlo analysis. To investigate resilience of proposed filter, cut-off frequency of the filter is analyzed under the Monte-Carlo seeds. The Monte-Carlo simulation runs including distinct process corners (ss, sf, fs, ff) also transistor mismatches by changing transistors' channel lengths and/or width independently. In the end of this process, it should be noted that standard deviation of the cutoff frequency is lower than 10%, where cut-off frequency of the designed filter is around 24Hz while standard deviation is 1.47Hz. In the Monte Carlo analysis, all process variations and mismatches are taken into consideration for 100 independent runs. Standard deviation of the designed filter for 1.47Hz while cut-off frequency is 24Hz. Table 3 gives the detailed comparison of the proposed circuit with other studies in the literature. The design is considered to give promising results when compared to the defined Figure of Merit given in (9).

$$FoM = \frac{power}{dynamic\ range\ x\ order} \tag{9}$$

**Table 2**. Biasing current versus  $f_{-3dB}$

| $I_{B1}$ | $I_{B2}$ | $I_{B3}$ | $f_{-3dB}$ |

|----------|----------|----------|------------|

| 0.1nA    | 0.1nA    | 0.1nA    | 500mHz     |

| 0.1nA    | 0.1nA    | 1nA      | 3Hz        |

| 0.1nA    | 1nA      | 0.1nA    | 9Hz        |

| 1nA      | 1nA      | 1nA      | 24Hz       |

| 1nA      | 1nA      | 10nA     | 65Hz       |

Figure 12. The reconfigurable output of the designed filter for different bias currents of three cascaded cells.

Figure 13. Monte Carlo analysis for  $f_{-3dB} = 24$ Hz.

**Table 3**. Comparison between conventional designs and the proposed work.

| Parameters     | [5]   | [16] | [41] | [42]  | [43] | [44] | [45] | This Work |

|----------------|-------|------|------|-------|------|------|------|-----------|

| $V_{DD}, V$    | 1     | 1.8  | 1.8  | 1     | 3    | ±0.8 | 0.9  | ±0.3      |

| Technology, μm | 0.18  | 0.18 | 0.18 | 0.18  | 0.35 | 0.25 | 0.13 | 0.18      |

| Power, µW      | 0.35  | 0.57 | 200  | 0.453 | 0.75 | 30   | 2.8  | 0.9nW     |

| DC gain, dB    | -8    | 0    | -6   | -9.5  | -6   | -5   | 5.9  | 0         |

| Filter order   | 5     | 4    | 5    | 5     | 4    | 5    | 4    | 2         |

| THD, dB        | -49.9 | -40  | -44  | -48.6 | -59  | -40  | -40  | -43       |

| Dynamic range, dB      | 49.8  | 56.06 | 52  | 50    | 54    | 65  | 43.22 | 78.2    |

|------------------------|-------|-------|-----|-------|-------|-----|-------|---------|

|                        |       |       |     |       |       |     |       |         |

| Bandwidth, Hz          | 50    | 50    | 250 | 250   | 40    | 253 | 52    | 50      |

|                        |       |       |     |       |       |     |       |         |

| IRN, μV <sub>rms</sub> | 97    | 109   | 266 | 340   | 500   | 36  | 24.4  | 9.09    |

| FoM                    | 0.226 | 0.224 | 100 | 0.286 | 0.374 | 3.3 | 4.83  | 0.00575 |

### 5. Conclusions

In this work, a new implementation for low-pass filter of biomedical data acquisition system developed with DTMOS technique is proposed. The active RC filter is designed with OTA based capacitor multiplier. The cascaded cell-based implementation is performed with the design of capacitor multiplier, which is very appropriate for the low power and low frequency applications where high multiplication factor is required. The proposed structure works with a supply voltage of  $\pm~0.3V$  and dissipates 0.98nW, whilst the occupation area of core circuit on chip is  $0.0083 mm^2$ . The input referred noise of the designed filter is presented around  $9.09 \mu V/sqrt(Hz)$ . All simulations are performed in Cadence environment with  $0.18 \mu m$  TSMC technology.

## Acknowledgments

There is no funding to support this work.

### **Authors' contributions**

First Author performs the mathematical calculations. Second author simulates the circuit in Cadence environment.

Both authors read and approved the final manuscript.

# **Competing interests**

The authors declare that they have no competing interests.

## **Ethics in Publishing**

There are no ethical issues regarding the publication of this study.

#### References

- [1] Aazam M., Zeadally S., and Harras K. A., (2018) Deploying fog computing in industrial internet of things and industry 4.0, IEEE Transactions on Industrial Informatics, vol. 14, no. 10, pp. 4674–4682.

- [2] Wan J., Tang S., Shu Z., Li D., Wang S., Imran M., and Vasilakos A., (2016) Software-defined industrial internet of things in the context of industry 4.0, IEEE Sensors Journal, vol. 16, no. 20, pp. 1–1.

- [3] Vittoz E. and Fellrath J., (1977) CMOS analog integrated circuits based on weak inversion

- operations, IEEE Journal of Solid-State Circuits, vol. 12, no. 3, pp. 224–231.

- [4] Kim H. S. and Cha H.-K., (2018) A low-noise biopotential CMOS amplifier IC using low-power two-stage Ota for Neural Recording Applications, Journal of Circuits, Systems and Computers, vol. 27, no. 05, p. 1850068.

- [5] Sun C.-Y., and Lee S.-Y., (2018) A fifth-order Butterworth Ota-C LPF with multiple-output differential-input OTA for ECG applications, IEEE Transactions on Circuits and Systems II: Express Briefs, vol. 65, no. 4, pp. 421–425.

- [6] Li Y., Poon C. C., and Zhang Y.-T., (2010) Analog integrated circuits design for processing physiological signals," IEEE Reviews in Biomedical Engineering, vol. 3, pp. 93–105.

- [7] Bano S., Narejo G. B., and Usman Ali Shah S. M., (2018) Low voltage low power single ended operational transconductance amplifier for low frequency applications, Wireless Personal Communications, vol. 106, no. 4, pp. 1875–1884.

- [8] Behrouj A. R., Ghorbani A. R., Ghaznavi-Ghoushchi M. B., and Jalali M., (2019) A low-power CMOS transceiver in 130nm for wireless sensor network applications, Wireless Personal Communications, vol. 106, no. 3, pp. 1015–1039.

- [9] Rout S. S., Acharya S., and Sethi K., (2018) A low phase noise gm -boosted DTMOS VCO design in 180nm CMOS technology, Karbala International Journal of Modern Science, vol. 4, no. 2, pp. 228–236.

- [10] Alaybeyoglu E., (2019) Implementation of capacitor multiplier with cell-based variable transconductance amplifier, IET Circuits, Devices & Eamp; Systems, vol. 13, no. 3, pp. 267–272.

- [11] Sawigun C. and Thanapitak S., (2018) A 0.9-nW, 101-Hz, and 46.3-Vrms IRN Low-Pass Filter for ECG Acquisition Using FVF Biquads, IEEE Transactions on Very Large Scale Integration (VLSI) Systems, vol. 26, no. 11, pp. 2290–2298.

- [12] Hou Y., Yousef K., Atef M., Wang G., and Lian Y., (2018) A 1-to-1-khz, 4.2-to-544-NW, multi-level comparator based level-crossing ADC for IoT applications, IEEE Transactions on Circuits and Systems II: Express Briefs, vol. 65, no. 10, pp. 1390–1394.

- [13] Kaur A., Agarwal A., Agarwal R., and Kumar S., (2018) A novel approach to ECG R-peak detection," Arabian Journal for Science and Engineering, vol. 44, no. 8, pp. 6679–6691.

- [14] Ozenli D., Alaybeyoglu E., and Kuntman H., (2021)"A grounded capacitance multiplier circuit employing VDTA, 2021 13th International Conference on Electrical and Electronics Engineering (ELECO), pp. 38–41.

- [15] Harrison R. R., (2007) A versatile integrated circuit for the acquisition of Biopotentials, IEEE Custom Integrated Circuits Conference, pp. 115–122.

- [16] Machha Krishna J. R. and Laxminidhi T., (2019) Widely tunable low-pass gm-C filter for

- biomedical applications., IET Circuits, Devices & Systems, vol. 13, no. 2, pp. 239–244.

- [17] Nagaraj K., (1989) A parasitic-insensitive area-efficient approach to realizing very large time constants in switched-capacitor circuits, IEEE Transactions on Circuits and Systems, vol. 36, no. 9, pp. 1210–1216.

- [18] Solis-Bustos S., Silva-Martinez J., Maloberti F., and Sanchez-Sinencio E., (2000) A 60-DB dynamic-range CMOS sixth-order 2.4-Hz low-pass filter for medical applications, IEEE Transactions on Circuits and Systems II: Analog and Digital Signal Processing, vol. 47, no. 12, pp. 1391–1398.

- [19] Veeravalli A., Sanchez-Sinencio E., and Silva-Martinez J., (2002) Transconductance amplifier structures with very small transconductances: A comparative design approach, IEEE Journal of Solid-State Circuits, vol. 37, no. 6, pp. 770–775.

- [20] Zhou L. and Chakrabartty S., (2015) Design of low-Gm transconductors using Varactor-based degeneration and linearization technique, IEEE Biomedical Circuits and Systems Conference (BioCAS), pp. 1-4.

- [21] Tanzawa T., (2010) On two-phase switched-capacitor multipliers with minimum circuit area, IEEE Transactions on Circuits and Systems I: Regular Papers, vol. 57, no. 10, pp. 2602–2608.

- [22] Yesil A., Yuce E., and Minaei S., (2017) Grounded capacitance multipliers based on active elements, AEU International Journal of Electronics and Communications, vol. 79, pp. 243–249.

- [23] Abuelma'atti M. T. and Tasadduq N. A., (1999) Electronically tunable capacitance multiplier and frequency-dependent negative-resistance simulator using the current-controlled current conveyor, Microelectronics Journal, vol. 30, no. 9, pp. 869–873.

- [24] Prommee P. and Somdunyakanok M., (2011) CMOS-based current-controlled DDCC and its applications to capacitance multiplier and Universal Filter, AEU International Journal of Electronics and Communications, vol. 65, no. 1, pp. 1–8.

- [25] Khan A. A., Bimal S., Dey K. K., and Roy S. S., (2002) Current conveyor based R- and C- multiplier circuits, AEU International Journal of Electronics and Communications, vol. 56, no. 5, pp. 312–316.

- [26] Das B. P., Watson N. and Liu Y., (2010) Wide tunable all pass filter using OTA as active component". IEEE International Conference on Signals and Electronic Circuits, pp. 379-382.

- [27] Liu P.-J., Hsu C.-Y., and Chang Y.-H., (2015) Techniques of dual-path error amplifier and capacitor multiplier for on-chip compensation and soft-start function, IEEE Transactions on Power Electronics, vol. 30, no. 3, pp. 1403–1410.

- [28] Sagbas M., Ayten U. E., Sedef H., and Koksal M., (2009) Electronically tunable floating

- inductance simulator," AEU International Journal of Electronics and Communications, vol. 63, no. 5, pp. 423–427.

- [29] Shin S.-H., Kweon S.-J., Jo S.-H., Choi Y.-C., Lee S., and Yoo H.-J., (2015) A 0.7-MHz–10-MHz CT+ DT hybrid baseband chain with improved passband flatness for LTE application, IEEE Transactions on Circuits and Systems I: Regular Papers, vol. 62, no. 1, pp. 244–253.

- [30] Rincon-Mora G. A., (2000) Active capacitor multiplier in Miller-compensated circuits, IEEE Journal of Solid-State Circuits, vol. 35, no. 1, pp. 26–32.

- [31] Shukla P. and Gupta A., (2017) Current-mode PMOS capacitance multiplier, IEEE International Conference on Inventive Systems and Control (ICISC), pp. 1–4.

- [32] Achigui H. F., Fayomi C. J. B., and Sawan M., (2006) 1-V DTMOS-based class-AB operational amplifier: Implementation and experimental results, IEEE Journal of Solid-State Circuits, vol. 41, no. 11, pp. 2440–2448.

- [33] Uygur A. and Kuntman H., (2013) DTMOS-based 0.4 V ultra low-voltage low-power VDTA design and its application to EEG data processing, Radioengineering, vol. 22, no. 2, pp. 458-466.

- [34] Kalekar P., Vernekar P., Vasantha M. H., Kumar Y. B. N., and Bonizzoni E., (2018) A 0.5 V low power DTMOS OTA-C filter for ECG sensing applications, IEEE SENSORS, pp. 1-4.

- [35] Srivastava P., Gupta R. K., Sharma R. K. and Ranjan R. K., (2020) MOS-only Memristor emulator, Circuits, Systems, and Signal Processing, vol. 39, no. 11, 5848-5861.

- [36] Lorenzo R. and Chaudhury S., (2017) Dynamic threshold sleep transistor technique for high speed and low leakage in CMOS circuits, Circuits, Systems, and Signal Processing, 36(7), 2654-2671.

- [37] Tsividis Y. and McAndrew C., (2011) Operation and Modeling of the MOS Transistor, Oxford Univ. Press.

- [38] Parke S. A., Hu C., and Ko P. K., (1993) Bipolar-fet hybrid-mode operation of quarter-micrometer SOI mosfets (MESFETs read MOSFETs), IEEE Electron Device Letters, vol. 14, no. 5, pp. 234–236.

- [39] Alaybeyoğlu E. and Kuntman H., (2019) Capacitor multiplier with high multiplication factor for integrated low pass filter of biomedical applications using DTMOS technique, AEU-International Journal of Electronics and Communications, vol. 107, pp. 291-297.

- [40] Alaybeyoğlu E. and Kuntman H., (2018) A new implementation of the reconfigurable analog baseband low pass filter with cell-based variable transconductance amplifier, Analog Integrated Circuits and Signal Processing, vol. 97, no. 1, pp. 87-96.

- [41] Lo T.-Y. and Hung C.-C., (2007) A wide tuning range Gm-C continuous-time analog filter,

- IEEE Transactions on Circuits and Systems I: Regular Papers, vol. 54, no. 4, pp. 713–722.

- [42] Lee S.-Y. and Cheng C.-J., (2009) Systematic design and modeling of a OTA-C filter for portable ECG detection," IEEE Transactions on Biomedical Circuits and Systems, vol. 3, no. 1, pp. 53–64.

- [43] Liu Y.-T., Lie D. Y. C., Hu W., and Nguyen T., (2012) An ultralow-power CMOS transconductor design with wide input linear range for biomedical applications, IEEE International Symposium on Circuits and Systems, pp. 2211–2214.

- [44] Mahmoud S. A., Bamakhramah A., and Al-Tunaiji S. A., (2013) Low-noise low-pass filter for ECG portable detection systems with digitally programmable range, Circuits, Systems, and Signal Processing, vol. 32, no. 5, pp. 2029–2045.

- [45] Arya R. and Oliveira J. P., (2016) Gm-C biquad filter for low signal sensor applications, 23rd International Conference Mixed Design of Integrated Circuits and Systems, pp. 207–210.